Elemen penyimpan (memori) yang beroperasi dengan level-level sinyal (High dan Low) disebut sebagai latch. Baik latch maupun flip-flop saling berkaitan karena rangkaian dasar dari flip-flop tersusun dari latch. Meskipun latch bermanfaat dalam menyimpan informasi biner juga dalam mendesain rangkaian berurut tak sinkron (asynchronus sequential circuits) tapi latch tidak praktis jika dijadikan sebagai elemen penyimpan pada rangkaian berurut (sequential circuit). Ada dua jenis latch, SR latch dan D Latch.

SR Latch

SR latch adalah rangkaian berurut yang dapat dibuat dari rangkaian gerbang NOR terkopel atau gerbang NAND terkopel, SR latch memiliki dua input yaitu S berarti set dan R berarti reset.

SR latch dari gerbang NOR

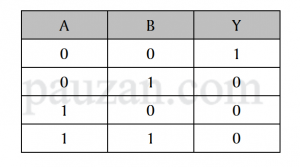

Sebelum kita membahas tabel kebenaran untuk SR latch, terlebih dahulu kita membuat tabel kebenaran untuk gerbang NOR dengan dua input, perhatikan tabel berikut ini:

Tabel 1. Tabel kebenaran NOR

Berdasarkan tabel 1, maka dapat disimpulkan:

- output Y hanya bernilai 1 jika kedua inputnya (A dan B) bernilai 0

- jika salah satu input (A atau B) bernilai 1 maka outputnya (Y) pasti 0

poin a dan b di atas kita jadikan sebagai rujukan dalam membuat tabel kebenaran untuk SR latch yang menggunakan gerbang NOR.

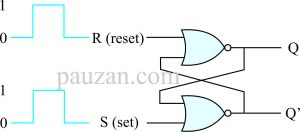

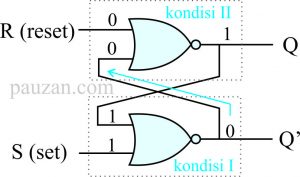

SR latch yang disusun dari dua gerbang NOR dapat dilihat pada gambar di bawah ini:

Gambar 1. SR latch menggunakan gerbang NOR

Sekarang kita kombinasikan nilai input S dan R;

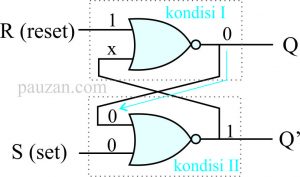

1. jika S=0 dan R=1

Salah satu input yaitu R bernilai 1, sesuai dengan poin b di atas (jika salah satu input bernilai 1 maka pasti outputnya 0, tidak perduli kondisi input yang lainnya). maka otuput Q bernilai 0, sehingga input pada gerbang NOR yang dibawah menjadi 0 (dari S) dan 0 (input berasal dari Q), jika melihat tabel kebenaran NOR di atas maka nilai output Q’ adalah 1. Perhatikan gambar berikut:

Gambar 2. Alur memperoleh Q dan Q’ dari S=0, R=1

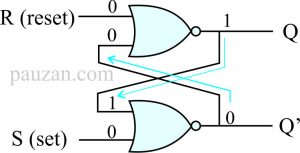

sekarang kita matikan semua input, ini berarti S=0 dan R=0, kondisi pada gambar 2 menjadi:

Gambar 3. Kondisi setelah input S dan R dimatikan

Pada gambar 3, input pada gerbang NOR yang di atas terdiri dari 0 (dari R) dan 1 (dari Q’). Mengacu pada tabel kebenaran NOR maka output Q bernilai 0, sekarang Q ini menjadi input pada gerbang NOR yang di bawah. Input yang di bawah menjadi 0 (dari S) dan 0 (dari Q) maka outputnya, Q’ adalah 1.

Perhatikan bahwa meskipun input S dan R dimatikan, nilai Q dan Q’ tidak berubah. maka inilah yang disebut sebagai memori (menyimpan) informasi biner. Kesimpulannya jika S=0, R=1 maka outputnya Q=0, Q’=1. Kondisi ini tidak berubah meskipun S dan R dimatikan (S=0, R=0).

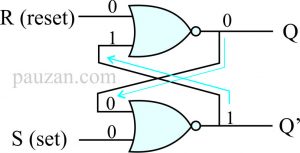

2. jika S=1 dan R=0

salah satu input yaitu S bernilai 1, sesuai dengan poin b di atas (jika salah satu input bernilai 1 maka pasti outputnya 0, tidak perduli kondisi input yang lainnya). maka otuput Q’ bernilai 0, sehingga input pada gerbang NOR yang di atas menjadi 0 (dari R) dan 0 (input berasal dari Q’), jika melihat tabel kebenaran NOR di atas maka nilai output Q adalah 1. Perhatikan gambar berikut:

Gambar 4. Alur memperoleh Q dan Q dari S=1, R=0

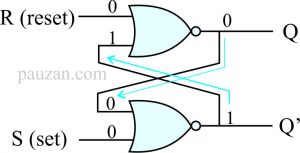

Sekarang kita matikan semua input, ini berarti S=0 dan R=0, kondisi pada gambar 2 menjadi:

Gambar 5. Kondisi setelah input S dan R dimatikan

Pada gambar 5, input pada gerbang NOR yang di bawah terdiri dari 0 (dari S) dan 1 (dari Q). Mengacu pada poin b, jika salah satu input bernilai 1 maka pasti outputnya 0, maka output dari gerbang NOR ini adalah Q’=0. Sekarang Q’ ini menjadi input bersama dengan R=0 pada gerbang NOR yang di atas, karena keduanya 0 maka output dari gerbang NOR adalah Q=1.

Perhatikan bahwa meskipun input S dan R dimatikan, nilai Q dan Q’ tidak berubah. maka inilah yang disebut sebagai memori (menyimpan) informasi biner. Kesimpulannya jika S=1, R=0 maka outputnya Q=1, Q’=0. Kondisi ini tidak berubah meskipun S dan R dimatikan (S=0, R=0)

3. Jika S=1 dan R=1

Kita mulai analisis dari S=1, boleh juga dari R=1 hasilnya akan sama.

Perhatikan gambar berikut:

Gambar 6. Uji output untuk S=1

Karena input pada gerbang NOR yang bawah salah satunya 1 (dari S) maka berdasarkan tabel kebenaran NOR (lihat poin b) sudah pasti outputnya 0 (Q’=0) tidak perduli apapun nilai input yang lainnya. Q’=0 sekarang menjadi input pada gerbang NOR yang atas, input yang lain adalah R=1, karena kedua inputnya 1 maka outputnya 0 (Q=0). Terjadi keanehan disini bahwa Q=Q’=0, hal ini tidak mungkin karena Q akan selalu berbeda dengan Q’. Maka keadaan ini disebut sebagai forbidden (dilarang).

Sekarang kita matikan semua input (S=0, R=0) maka rangkaiannya menjadi:

Gambar 7. S dan R dimatikan

Kita mulai dari output Q=0, Q kemudian menjadi input pada gerbang NOR yang di bawah, disini inputnya 0 (dari S) dan 0 (dari Q) maka dengan melihat tabel kebenaran NOR, outputnya adalah 1 (Q’=1). Sekarang Q’ menjadi input pada NOR yang di atas, maka inputnya 1 (dari Q’) dan 0 (dari R), mengacu pada tabel kebenaran maka outputnya adalah 0 (Q=0).

Perhatikan bahwa sebelum S dan R dimatikan kondisi Q=0, Q’=0. Setelah S dan R dimatikan kondisinya menjadi Q=0, Q’=1. Jadi terjadi perubahan keadaan dan tentu saja hal seperti ini tidak bisa dijadikan memori.

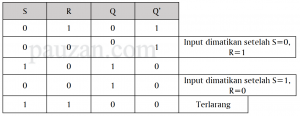

Jika kita buat tabel kebenaran SR latch dari poin 1 sampai dengan poin 3, maka tabelnya adalah sebagai berikut:

Tabel 2. Tabel kebenaran SR latch menggunakan gerbang NOR

Back: Pengertian Rangkaian Berurut

Next:

Video SR latch dengan gerbang NOR